DRAM refresh & PASR

You can think of DRAM like a big array of buckets for storing electrical charge. Every bucket represents a single binary digit. If the bucket is full, we have a 1, if its less than a certain capacity we have a 0.

Unfortunately, the buckets can leak pretty quickly and retaining the content is what this post is all about. The buckets we should probably call capacitors. The array is an integrated circuit. This post is concerned with how we retain the "data" despite the energy constantly dissipating from the cell.

It goes something like this:

During the active operation of a Windows device the contents of system memory (our buckets) are maintained through a process called “automatic refresh”. It also gets a zap when the DRAM is ‘touched’ through via a “normal” read or write.

(It is interesting to note that read operations from DRAM are destructive; during a read the charge is removed from the cell, and the sense amplifiers on the chip rewrite the cell in much the same way a write operation would occur ).

The amount of time between automatic refreshes is specific to the DRAM type but it is usually expressed in milliseconds. (As an example, automatic refresh is required at least every 64ms in the DDR2 specification ).

The automatic refresh operation is responsible for a large portion of the total system power cost during active (screen on) device use.

During screen off, or standby, a different approach is taken although memory refresh can still be a significant part of the total standby power consumption.

Self-refresh, sometimes referred to as IDD6 is a DRAM power mode where the memory controller clock is deactivated to reduce the power consumption of the system.

During self-refresh the DRAM automatically executes a refresh operation using the internal DRAM refresh counter rather than relying on the memory controller clock to signal an automatic refresh.

In the context of a Windows system ‘standby’ is during sleep (S3) or Connected Standby. Both low power modes require the contents of system memory to be maintained. This is in contrast to ‘Hibernate’ (S4) mode where the contents of memory are saved to the hard disk and the DRAM turned off with the rest of the system. S4 has a considerable impact on the time taken to wake the device compared to sleep but an improvement in standby capacity because the DRAM refresh is disabled once the memory content is saved to disk.

In addition to the self-refresh mode there are a series of power management features defined in the DRAM specifications and implemented by some DRAM manufacturers to further reduce the power consumption of a device during standby.

Some of the advanced power features for memory are enabled and configured during DRAM or system manufacture, others may be exposed via system firmware and controlled and optimized by the operating system in partnership with the device manufacturer.

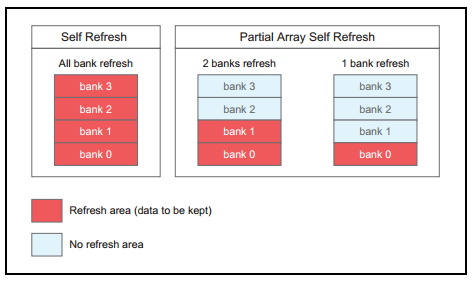

Partial Array Self Refresh (PASR) is one such feature. PASR allows portions of a memory array to be put into a no refresh state while the device is operating in standby.

Typically the entire memory array is put into self-refresh during standby because there is the hardware has no knowledge of memory content, no way to determine which pages are important to the system. The assumption must be that the entire DRAM array contains important data.

Using PASR the Operating System should intelligently place data during active use so that only a portion of the DRAM requires self-refresh during standby (because the OS has grouped memory pages in an efficient way).

In the example below memory pages are placed in bank 1 and bank 0 only, allowing self-refresh to be disabled on the other banks during standby.

In the LP-DDR3 JEDEC specification PASR uses two registers to control which memory banks, and which segments should be refreshed during standby.

- Mode Register 16 (MR16), the bank mask

- Mode Register 17 (MR17), the segment mask

DRAM modules that support PASR are divided into Banks and Segments.

A DRAM module typically contains 8 banks and each bank is broken into 8 segments.

The PASR registers MR16, and MR17 contain 8 bits each. The 8 bits in each register line up with the 8 banks, and 8 segments of those banks. In this way, the register provides a mask of the banks requiring self-refresh and which do not. The registers can be manipulated by the memory controller to control which banks should be refreshed at a given time.

It is important to note that there is not an individual register for each bank. This would mean that the granularity offered by this bitmask is not individual segments on individual banks, but rather – the same segments on every bank if the segment mask (MR17) is in use.

Another interesting point is that in the specification, the PASR mode registers are documented as write only. There is no interface to determine the current value of the registers; only to write the value. So the system would need to maintain knowledge of the banks currently being self refreshed.

It sounds really interesting. I should mention, I don't actually know of a system that is actively using PASR yet. That's not to say they don't exist, i just haven't found one. I will add a reference to this post if/when i do.

Before i sign off, there is another self-refresh feature called Temperature Controlled Self Refresh (TCSR) worth a quick introduction:

TCSR is based on the idea is that the electrical charge in DRAM dissipates at a lower rate when a device is cool. So, as the device cools down during sleep we wont need to charge the DRAM cells as frequently. So, in the (LP-DDR) specifications for DRAM there is a feature (TCSR) which is able to detect when the device has cooled down to actively reduce the self-refresh frequency. This give us longer battery life. Neat.

The real point of this post - references for DRAM refresh:

JEDEC DDR3 Specification

https://www.jedec.org/standards-documents/docs/jesd-79-3d

JEDEC DDR2 Specification

https://www.jedec.org/standards-documents/docs/jesd-79-2e

JEDEC LP-DDR3 Specification

https://www.jedec.org/sites/default/files/docs/JESD209-3.pdf

JEDEC LP-DDR2 Specification

https://www.jedec.org/sites/default/files/docs/JESD209-2B.pdf

Temperature Controlled Self Refresh: Micron

https://www.elpida.com/pdfs/E0599E20.pdf

PASR Reference: Micron

https://www.elpida.com/pdfs/E0597E10.pdf

Deep Power Down Whitepaper: Micron

https://www.elpida.com/pdfs/E0598E21.pdf

Elpida Memory FAQ:

https://www.elpida.com/en/products/faq.html#tech-dr

Micron: Low-Power versus Standard DDR SDRAM

https://download.micron.com/pdf/technotes/DDR/tn4615.pdf

LP-DDR2 - the new mainstream for embedded and mobile applications?

https://www.denali.com/wordpress/index.php/dmr/2010/05/20/lpddr2-the-new-mainstream-memory-for-emb

Texas Instruments: Keystone Architecture for DDR3 Memory Controller

https://www.ti.com/lit/ug/sprugv8c/sprugv8c.pdf

Wiki: Mobile DDR

https://en.wikipedia.org/wiki/Mobile_DDR

ELPIDA: Low power function of Mobile RAM

https://www.elpida.com/pdfs/E0597E10.pdf

Research Paper: Trends in Low Power RAM circuit technologies

https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=371965

Data Sheets for LP-RAM from Micron

https://www.micron.com/products/dram/mobile-lpdram#fullPart&306=0